- True Dual-Role capability

- OTG high performance host mode

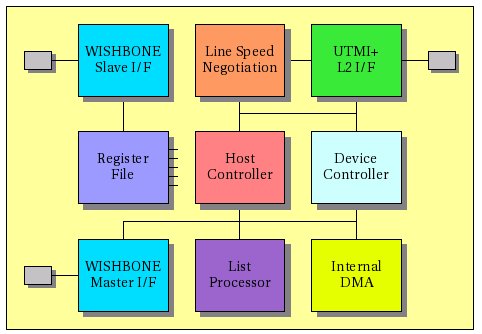

- UTMI+ L2 Interface, ULPI wrapper and FS only transceiver interface available

- Full USB peripheral support

- Session request protocol support

- Host negotiation protocol support

- High, Full and Low Speed mode support

- Up to 16 endpoints

- Bulk, interrupt and isochronous transfers

- Slave and Master System Interface:

- AVALON

- AHB

- OCP

- OPB

- PLB

- WISHBONE

- Customer specified bus interface

- No dedicated local memory required

- Compact and cost-effective solution for SoC

|

|